【电子书】芯粒(Chiplet)技术基础与工程师指南

- 2026-05-08 10:08:35

随着摩尔定律放缓和制程成本激增,半导体行业正经历从单片集成(Monolithic)向系统级封装及异构集成(HI)的战略转移。芯粒(Chiplet)技术通过将大芯片拆分为模块化的独立单元并重新组装,有效提升了良率并降低了开发成本。由Semiconductor Engineering汇编发布的《面向初学者的芯粒技术指南》电子书重点分析了 UCIe 标准的互连架构、先进封装技术(如混合键合)、已知合格芯片(KGD)保障策略,以及开放生态系统面临的设计与安全挑战。

电子书要点:

·标准化互连: UCIe 已成为建立开放芯粒市场的基石,它不仅定义了物理层,还通过可管理层实现了跨厂商的热管理与电源管理。

·制造演进: 混合键合技术正将互连间距从微米级推进到亚微米级(<10 µm),彻底改变了 3D 堆叠的密度潜力。

·良率控制: 确保 KGD 是降低成本的关键,业界正转向使用牺牲焊盘、晶圆映射和智能遥测技术。

·行业瓶颈: 热管理、物理布局兼容性及供应链安全仍是实现“即插即用”开放市场的核心技术壁垒。

一、 UCIe 标准:芯粒互连与管理的通用语言

UCIe (Universal Chiplet Interconnect Express) 旨在解决不同厂商芯粒间的“互操作性”问题,其影响力不仅限于物理层传输,更涵盖了全栈式的管理功能。

1.1 协议层面的管理架构

UCIe 定义了一个可选的可管理层 (Manageability Layer),将散热与电源管理纳入标准化范畴:

·热管理功能: 芯粒必须能通过标准协议报告自身热状态并响应指令,允许系统软件统一调度工作状态(如动态调频调压),防止局部过热。

·遥测与监控 (Telemetry): 支持实时读取内部传感器数据,为系统集成商提供统一的调试与维护接口。

·电源管理: 将电源传输规范与热管理结合,从源头控制发热。

1.2 物理规格与通道配置

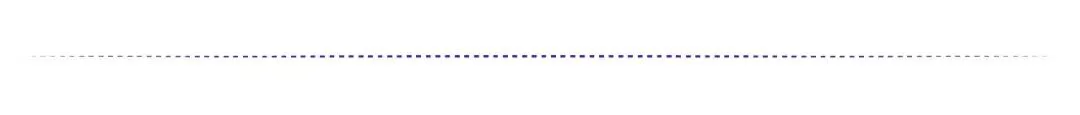

UCIe 针对不同应用场景定义了两套核心封装规格:

1.3 物理布局的灵活性:通道反转 (Lane Reversal)

为了解决不同厂商芯粒旋转布局导致的引脚顺序颠倒问题,UCIe 引入了通道反转技术。这允许设计者在物理布线顺序相反的情况下,通过协议初始化阶段的逻辑映射修正差异,极大地赋予了布局规划(Floorplanning)的灵活性。

二、 关键制造技术:混合键合与 3D 集成

混合键合(Hybrid Bonding)被视为实现高性能 3D-IC 的核心技术,通过消除焊料(Solder)实现了原子级的直接结合。

2.1 技术突破与优势

·间距缩减: 传统微凸块(Microbump)间距通常在 10-50 µm,而混合键合可将其缩减至 0.4 – 10 µm。

·消除焊料限制: 采用铜对铜(Copper-to-Copper)连接,消除了焊料桥接导致短路的风险,不再需要为防止焊料溢出而预留空间。

·垂直空间优化: 混合键合消除了芯粒间的物理间隙,显著降低了堆叠高度,允许在相同空间内集成更多 HBM 层。

三、 良率与可靠性保障策略

三、 良率与可靠性保障策略在芯粒架构中,一个坏芯会导致整个封装组件报废。因此,确保已知合格芯片 (KGD) 是工程设计的首要任务。

3.1 测试与筛选技术

·牺牲测试焊盘 (Sacrificial Pads): 针对混合键合中铜触点极易受损的特性,设计专门用于探针接触的焊盘,确保真正的键合表面保持平整和清洁。

·智能晶圆映射 (Wafer Mapping): 贴片机读取预先生成的晶圆图,仅将合格的顶层芯粒堆叠到合格的底层芯片上,避免资源浪费。

·离群值检测: 利用片上监控技术(如 proteanTecs)进行参数分级,识别处于性能边缘的“弱”芯粒,提升预组装质量。

3.2 可靠性考量

·热膨胀系数 (CTE) 不匹配: 不同材料在热循环中产生的应力可能导致翘曲(Warping)和连接失效。

·电迁移: 在高密度布线和高电流密度下,金属线存在电迁移风险。

四、 设计挑战:散热与布局优化

芯粒集成(尤其是 3D 堆叠)带来了极高的功率密度,传统的散热方法已面临瓶颈。

4.1 热管理考量

·热阱效应: 3D 堆叠中间层的热量被外层包裹,难以导出。

·热感知布局算法: 研究人员正开发基于扩散模型和自动微分的布局优化工具(如 DiffChip),旨在最小化总线长并确保热分布均匀。

4.2 互连拓扑优化

新兴研究如 PlaceIT 方法论,旨在联合优化芯粒放置与互连拓扑(ICI)。相较于 2D 骨干网,这种方法能根据流量特性(如缓存一致性流量)减少高达 62% 的延迟。

五、 安全与供应链风险

芯粒市场的开放性带来了新的安全挑战,攻击面从单片芯片内部扩展到了封装内的物理互连。

5.1 主要安全威胁

·高级封装漏洞: 包括硬件木马植入、边带攻击(通过电源噪声或电磁辐射泄露信息)以及通过有源中介层进行的攻击。

·物理探测风险: 封装内部的微小引脚虽难以接触,但非接触式的激光探测仍可能获取敏感信号。

·供应链伪造: 分散的供应商体系增加了伪造组件进入供应链的风险。

5.2 防御机制

·封装内流量加密: UCIe 和 BoW 都在探索标准化加密方案,但需平衡性能损耗。

·认证协议: 如针对安全测试的认证部分加密协议,确保敏感测试数据仅发送给授权芯粒。

六、 展望:迈向开放市场

六、 展望:迈向开放市场芯粒技术的最终愿景是像“乐高积木”一样即插即用,但实现这一愿景仍需克服以下障碍:

·全栈标准化: 除了物理连接,必须在初始化、固件下载、错误报告和安全机制上达成完全统一。

·技术演进: 包括光子集成芯粒(Photonic Chiplets)、玻璃基板封装以及无线互连技术的探索,有望进一步突破延迟和带宽瓶颈。

·应用领域: AI 加速器、大模型训练、自动驾驶汽车电子将是芯粒技术最先爆发的增长点。